2.3 创建第一个工程

2.3.1 新建一个工程

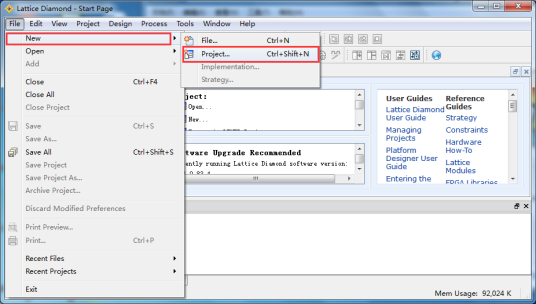

1、在Diamond软件面板上,选择File>New>Project,进行新工程创建。

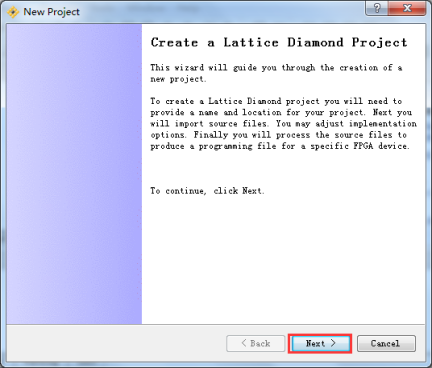

2、创建新工程,点击Next,开始工程设置。

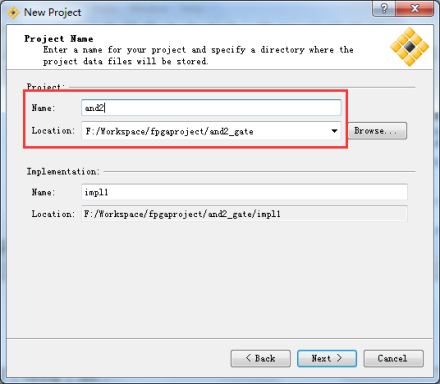

3、设置工程名称和工程所在路径,此处要注意:最好一个工程创建一个新建目录,否则所有相关文件均会在上一层目录中。如本例,若路径仅选择F:/Workspace/fpgaproject,则and2工程所有文件均保存在fpgaproject中。完成设置后点击Next。

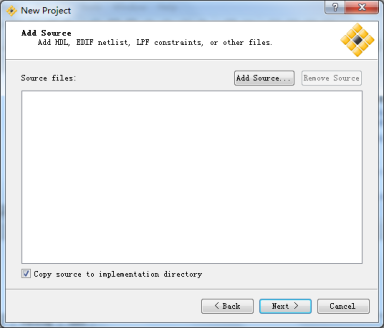

4、添加相关设计文件或约束文件。有必要提醒:如果从其他地方添加源文件务必勾选Copy source to implementation directory,否则修改会影响原文件。若无需添加则直接Next。

5、器件选择:LCMXO2-4000HC-4MG132C。务必按照下图所示选择。完成设置后点击Next。

6、综合工具选择,可以选择第三方综合工具Synplify Pro,也可使用原厂综合工具Lattice ISE,这里采用默认设置。直接Next。

7、当看到下图,说明工程创建已经完成。点击Finish就OK了。

2.3.2 添加设计文件

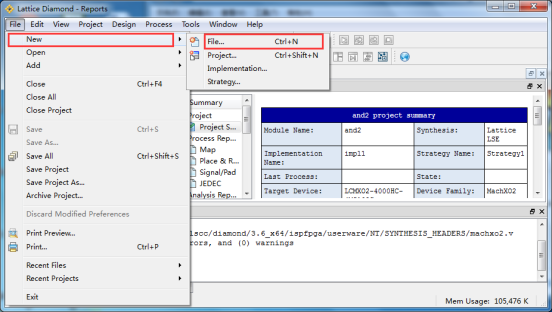

1、在Diamond软件面板上,选择File>New>File,进行新文件创建。

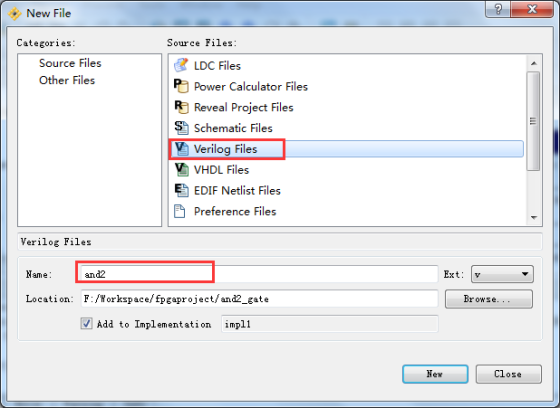

2、在文件创建界面,选择合适的文件类型。本文添加Verilog HDL设计文件。选好类型,设置文件名称。点击Yes,完成创建。

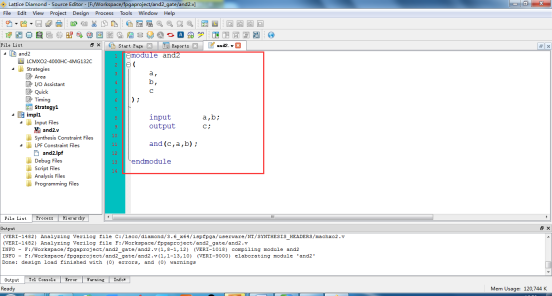

3、在新创建的Verilog文件中进行Verilog HDL代码编写。编写完成后,保存。IDE自动将模块更新到左侧Hierarchy(层次)窗口。

代码如下:

module and2

(

a,

b,

c

)

input a,b;

output c;

and(c,a,b);

endmodule

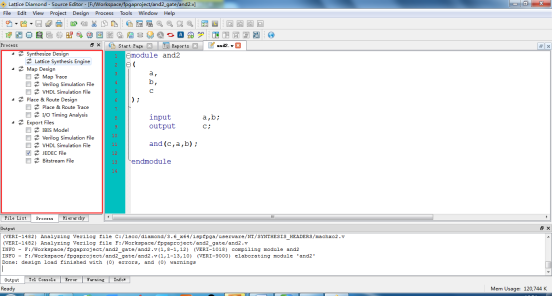

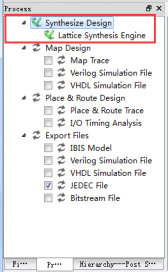

4、编写好代码,需要进行验证。在IDE左侧,选择Process。双击Synthesis Design,对设计进行综合。

若设计没有问题,在选项前面会有绿色的对号,如果出现错误,则要在排除错误之后才能继续进行。

2.3.3 管脚分配

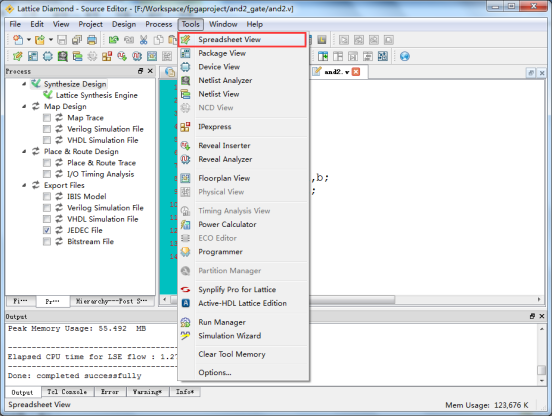

1、在工具栏中选择第三行第一个图标,点击即可进入管脚分配界面。

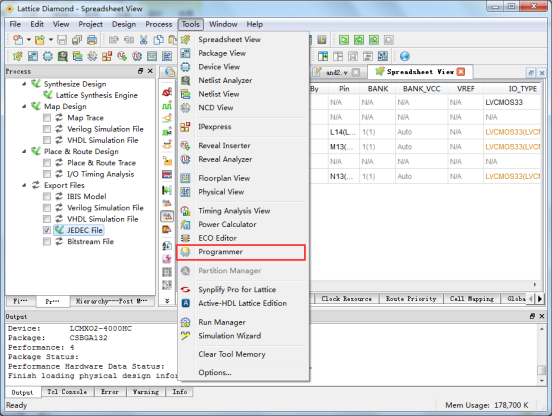

或者选择Tools->Spreadsheet View

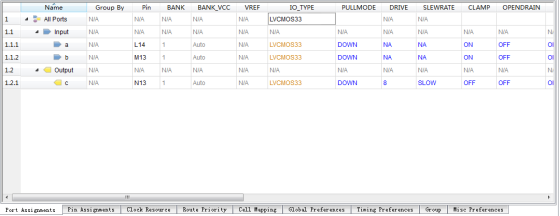

2、管脚设计需要的约束如下。输入信号a,b对应板卡上按键K1,K2,也就是FPGA的管脚L14和M13。输出信号c对应板卡上的LED1,也就是FPGA的管脚N13。IO_TYPE栏的电气信号可以修改成LVCMOS33(3.3V电平),完成设置后,Ctrl+S保存设置。

2.3.4 生成编译文件与下载

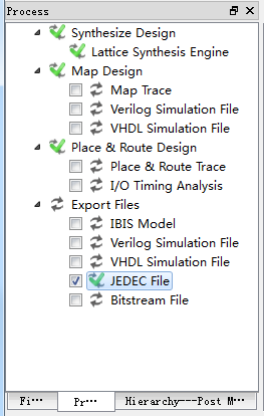

1、由于本设计极其简单,故没有将仿真、布局布线、生成编译文件一步一步介绍给大家。在此,想告诉大家,若设计简单可直接生成编译文件。

2、完成编译后,则可以将编译��文件下载到板卡上测试了。选择工具栏第三行图标。

也可以选择Tools->Programmer,

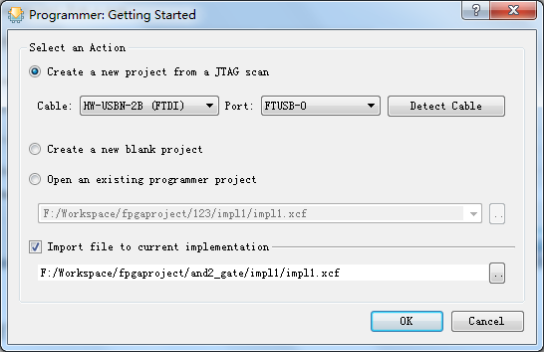

3、在进入FPGA编程前,IDE会检测调试工具,如下图。调试工具正确安装驱动后,会自动识别,因此选择默认即可。

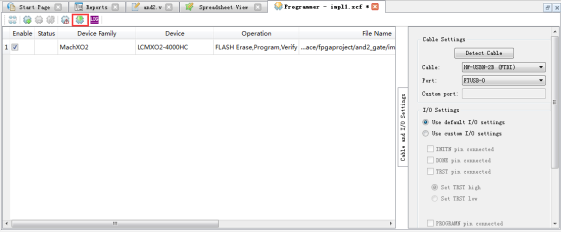

4、进入编程下载界面后,点击界面中图标。

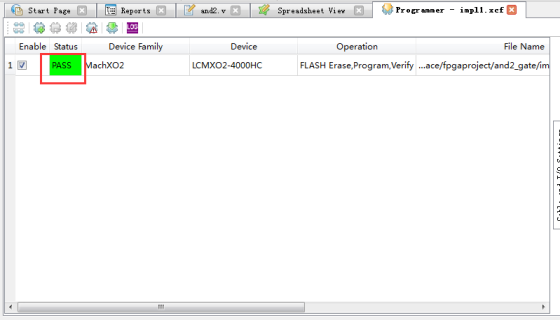

5、下载完成后,界面显示PASS。

至此,新工程从创建到综合实现,再到编译下载都已完成。

接下来就是看看下载到小脚丫上的程序运行结果了。实例是一个简单的二输入与门逻辑,利用两个按键(key1、key2)来控制LED灯(led1)的亮灭。在FPGA板上led1的信号为高时,led1不亮;当led1的信号为低时,led1点亮。而按键key1和key2初始状态是高,当按键按下时信号变低。所以程序运行后,按任意一个键或者两个键同时按下,led1变亮;否则的话,led1应该不亮。

2.3.5 小结

总结一下FPGA的一般开发步骤:

1、建立工程,包括工程路径、芯片选型

2、源文件输入,一般有图形和文本输入两种方式,文本的话,一般公司使用Verilog较多

3、编译综合(Synthesis),将行为和功能层次表达的电子系统转化为低层次模块的组合,一般可以查看系统的RTL层次图

4、添加约束,包括分配管脚,可以使用图形和文本输入两种方式

5、实现(Implementation),实现逻辑网表文件,布局布线

6、验证(Verification),包括时序仿真和功能仿真,一般会结合ModelSim或者Active-HDL编写testbench进行测试

7、生成下载的bitstream文件

8、下载工程文件到开发板,包括仿�真器连接和配置

9、效果演示

比较简单的工程可以省略其中的一些步骤,直接上板看效果。